# **SEMESTER IV**

| SLOT | COURSE<br>NO. | COURSES                                         | L-T-P | HOURS | CREDIT |

|------|---------------|-------------------------------------------------|-------|-------|--------|

| A    | MAT 206       | GRAPH THEORY                                    | 3-1-0 | 4     | 4      |

| В    | CST 202       | COMPUTER ORGANISATION<br>AND ARCHITECTURE       | 3-1-0 | 4     | 4      |

| С    | CST 204       | DATABASE MANAGEMENT<br>SYSTEMS                  | 3-1-0 | 4     | 4      |

| D    | CST 206       | OPERATING SYSTEMS                               | 3-1-0 | 4     | 4      |

| Е    | EST 200       | DESIGN & ENGINEERING                            | 2-0-0 | 2     | 2      |

| F    | MNC 202       | CONSTITUTION OF INDIA                           | 2-0-0 | 2     |        |

| S    | CSL 202       | DIGITAL LAB                                     | 0-0-3 | 3     | 2      |

| T    | CSL204        | OPERATING SYSTEMS LAB                           | 0-0-3 | 3     | 2      |

| Н    | CST 294       | COMPUTATIONAL FUNDAMENTALS FOR MACHINE LEARNING | 3-1-0 | 4     | 4      |

|      |               | TOTAL                                           |       | 26*   | 22/26  |

<sup>\*</sup> Excluding Hours to be engaged for Remedial/Minor/Honors course.

| CODE    | COURSE NAME  | CATEGORY | L | Т | P | CREDIT |

|---------|--------------|----------|---|---|---|--------|

| MAT 206 | GRAPH THEORY | BSC      | 3 | 1 | 0 | 4      |

**Preamble:** This course introduces fundamental concepts in Graph Theory, including properties and characterisation of graph/trees and graph theoretic algorithms, which are widely used in Mathematical modelling and has got applications across Computer Science and other branches in Engineering.

**Prerequisite:** The topics covered under the course Discrete Mathematical Structures (MAT 203)

Course Outcomes: After the completion of the course the student will be able to

| CO 1 | Explain vertices and their properties, types of paths, classification of graphs and trees & their properties. (Cognitive Knowledge Level: Understand)                                                        |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CO 2 | Demonstrate the fundamental theorems on Eulerian and Hamiltonian graphs. (Cognitive Knowledge Level: Understand)                                                                                             |  |  |  |  |  |

| CO 3 | Illustrate the working of Prim's and Kruskal's algorithms for finding minimum cost spanning tree and Dijkstra's and Floyd-Warshall algorithms for finding shortest paths. (Cognitive Knowledge Level: Apply) |  |  |  |  |  |

| CO 4 | Explain planar graphs, their properties and an application for planar graphs.  (Cognitive Knowledge Level: Apply)                                                                                            |  |  |  |  |  |

| CO 5 | Illustrate how one can represent a graph in a computer. (Cognitive Knowledge Level: Apply)                                                                                                                   |  |  |  |  |  |

| CO 6 | Explain the Vertex Color problem in graphs and illustrate an example application for vertex coloring. (Cognitive Knowledge Level: Apply)                                                                     |  |  |  |  |  |

# Mapping of course outcomes with program outcomes

|      | PO<br>1   | PO 2      | PO 3         | PO 4         | PO<br>5 | PO<br>6   | PO 7 | PO<br>8 | PO<br>9 | PO 10     | PO 11 | PO 12     |

|------|-----------|-----------|--------------|--------------|---------|-----------|------|---------|---------|-----------|-------|-----------|

| CO 1 | √         | √         | √            |              |         |           |      |         |         | √         |       | √         |

| CO 2 | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$    | $\checkmark$ |         |           |      |         |         | $\sqrt{}$ |       | $\sqrt{}$ |

| CO 3 |           | √         | $\sqrt{}$    | $\sqrt{}$    |         |           |      |         |         | √         |       | √         |

| CO 4 | √         | √         | √            | $\sqrt{}$    |         |           |      |         |         | $\sqrt{}$ |       | √         |

| CO 5 | $\sqrt{}$ | $\sqrt{}$ | $\checkmark$ |              |         |           |      |         |         | $\sqrt{}$ |       | $\sqrt{}$ |

| CO 6 |           | √         |              |              |         | $\sqrt{}$ |      |         |         | $\sqrt{}$ |       | V         |

| Abstract POs defined by National Board of Accreditation |                                            |      |                                |  |  |  |  |

|---------------------------------------------------------|--------------------------------------------|------|--------------------------------|--|--|--|--|

| PO#                                                     | Broad PO                                   | PO#  | CAL Broad PO                   |  |  |  |  |

| PO1                                                     | Engineering Knowledge                      | PO7  | Environment and Sustainability |  |  |  |  |

| PO2                                                     | Problem Analysis                           | PO8  | Ethics                         |  |  |  |  |

| PO3                                                     | Design/Development of solutions            | PO9  | Individual and team work       |  |  |  |  |

| PO4                                                     | Conduct investigations of complex problems | PO10 | Communication                  |  |  |  |  |

| PO5                                                     | Modern tool usage                          | PO11 | Project Management and Finance |  |  |  |  |

| PO6                                                     | The Engineer and Society                   | PO12 | Life long learning             |  |  |  |  |

# **Assessment Pattern**

| Bloom's Category  | Continuous Assessr | End Semester |                 |

|-------------------|--------------------|--------------|-----------------|

| Broom a Carregory | 1                  | 2            | Examination (%) |

| Remember          | 30                 | 30           | 30              |

| Understand        | 30                 | 30           | 30              |

| Apply             | 40                 | 40           | 40              |

| Analyse           |                    |              |                 |

| Evaluate          |                    |              |                 |

| Create            |                    |              |                 |

#### **Mark Distribution**

| Total Marks | Total Marks CIE Marks |     | ESE Duration |  |  |

|-------------|-----------------------|-----|--------------|--|--|

| 150         | 50                    | 100 | 3 hours      |  |  |

#### **Continuous Internal Evaluation Pattern:**

Attendance : 10 marks

Continuous Assessment Tests : 25 marks

Continuous Assessment Assignment: 15 marks

#### **Internal Examination Pattern:**

Each of the two internal examinations has to be conducted out of 50 marks

First Internal Examination shall be preferably conducted after completing the first half of the syllabus and the Second Internal Examination shall be preferably conducted after completing remaining part of the syllabus.

There will be two parts: Part A and Part B. Part A contains 5 questions (preferably, 2 questions each from the completed modules and 1 question from the partly covered module), having 3 marks for each question adding up to 15 marks for part A. Students should answer all questions from Part A. Part B contains 7 questions (preferably, 3 questions each from the completed modules and 1 question from the partly covered module), each with 7 marks. Out of the 7 questions in Part B, a student should answer any 5.

**End Semester Examination Pattern:** There will be two parts; Part A and Part B. Part A contain 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which student should answer anyone. Each question can have maximum 2 sub-divisions and carries 14 marks.

# **Syllabus**

#### Module 1

Introduction to Graphs: Introduction- Basic definition – Application of graphs – finite, infinite and bipartite graphs – Incidence and Degree – Isolated vertex, pendant vertex and Null graph. Paths and circuits – Isomorphism, sub graphs, walks, paths and circuits, connected graphs, disconnected graphs and components.

#### Module 2

**Eulerian and Hamiltonian graphs**: Euler graphs, Operations on graphs, Hamiltonian paths and circuits, Travelling salesman problem. Directed graphs – types of digraphs, Digraphs and binary relation, Directed paths, Fleury's algorithm.

#### Module 3

**Trees and Graph Algorithms**: Trees – properties, pendant vertex, Distance and centres in a tree - Rooted and binary trees, counting trees, spanning trees, Prim's algorithm and Kruskal's algorithm, Dijkstra's shortest path algorithm, Floyd-Warshall shortest path algorithm.

#### Module 4

Connectivity and Planar Graphs: Vertex Connectivity, Edge Connectivity, Cut set and Cut Vertices, Fundamental circuits, Planar graphs, Kuratowski's theorem (proof not required), Different representations of planar graphs, Euler's theorem, Geometric dual.

#### Module 5

**Graph Representations and Vertex Colouring**: Matrix representation of graphs-Adjacency matrix, Incidence Matrix, Circuit Matrix, Path Matrix. Coloring- Chromatic number, Chromatic polynomial, Matchings, Coverings, Four color problem and Five color problem. Greedy colouring algorithm.

#### Text book:

1. Narsingh Deo, Graph theory, PHI,1979

#### **Reference Books:**

- **1.** R. Diestel, *Graph Theory*, free online edition, 2016: diestel-graph-theory.com/basic.html.

- 2. Douglas B. West, Introduction to Graph Theory, Prentice Hall India Ltd.,2001

- 3. Robin J. Wilson, Introduction to Graph Theory, Longman Group Ltd.,2010

- 4. J.A. Bondy and U.S.R. Murty. Graph theory with Applications

# **Sample Course Level Assessment Questions.**

## **Course Outcome 1 (CO1):**

- 1. Differentiate a walk, path and circuit in a graph.

- 2. Is it possible to construct a graph with 12 vertices such that two of the vertices have degree 3 and the remaining vertices have degree 4? Justify

- 3. Prove that a simple graph with n vertices must be connected, if it has more than  $\frac{(n-1)(n-2)}{2}$  edges.

- 4. Prove the statement: If a graph (connected or disconnected) has exactly two odd degree, then there must be a path joining these two vertices.

# **Course Outcome 2 (CO2):**

- 1. Define Hamiltonian circuit and Euler graph. Give one example for each.

- 2. Define directed graphs. Differentiate between symmetric digraphs and asymmetric digraphs.

- 3. Prove that a connected graph G is an Euler graph if all vertices of G are of even degree.

- 4. Prove that a graph G of n vertices always has a Hamiltonian path if the sum of the degrees of every pair of vertices Vi, Vj in G satisfies the condition d(Vi) + d(Vj) = n 1

### **Course Outcome 3 (CO3):**

- 1. Discuss the centre of a tree with suitable example.

- 2. Define binary tree. Then prove that number of pendant vertices in a binary tree is  $\frac{(n+1)}{2}$

- 3. Prove that a tree with n vertices has n-1 edges.

- 4. Explain Floyd Warshall algorithm.

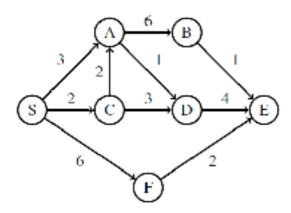

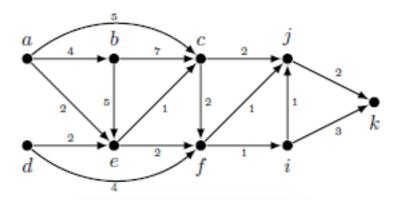

- 5. Run Dijkstra's algorithm on the following directed graph, starting at vertex S.

# **Course Outcome 4 (CO4):**

- 1. Define edge connectivity, vertex connectivity and separable graphs. Give an example for each.

- 2. Prove that a connected graph with n vertices and e edges has e n + 2 edges.

- 3. Prove the statement: Every cut set in a connected graph G must also contain at least one branch of every spanning tree of G.

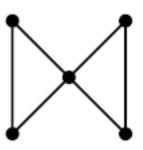

- 4. Draw the geometrical dual  $(G^*)$  of the graph given below, also check whether G and  $G^*$  are self-duals or not, substantiate your answer clearly.

# Course Outcome 5 (CO5):

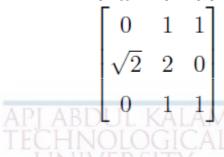

- 1. Show that if A(G) is an incidence matrix of a connected graph G with n vertices, then rank of A(G) is n-1.

- 2. Show that if **B** is a cycle matrix of a connected graph **G** with **n** vertices and **m** edges, then rank B = m n + 1.

- 3. Derive the relations between the reduced incidence matrix, the fundamental cycle matrix, and the fundamental cut-set matrix of a graph G.

- 4. Characterize simple, self-dual graphs in terms of their cycle and cut-set matrices.

#### **Course Outcome 6 (CO6):**

- 1. Show that an n vertex graph is a tree iff its chromatic polynomial is  $Pn(\lambda) = \lambda(\lambda 1)^{n-1}$

- 2. Prove the statement: "A covering g of a graph is minimal if g contains no path of length three or more."

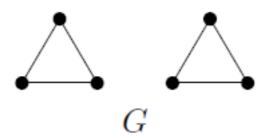

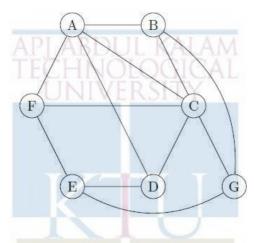

- 3. Find the chromatic polynomial of the graph

# **Model Question paper**

|        | QP Code: Total Pages:                                                                          | 4         |

|--------|------------------------------------------------------------------------------------------------|-----------|

| Reg No | : Name:                                                                                        |           |

|        | APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY IV SEMESTER B.TECH DEGREE EXAMINATION, MONTH and YEAR |           |

|        | Course Code: MAT 206                                                                           |           |

|        | Course Name: GRAPH THEORY                                                                      |           |

| Max. N | Tarks: 100 Duration: 3                                                                         | 3 Hours   |

|        | PART A                                                                                         |           |

|        | Answer all questions, each carries3 marks.                                                     | Mark<br>s |

| 1      | Construct a simple graph of 12 vertices with two of them having degree                         | , (3)     |

|        | three having degree 3 and the remaining seven having degree 10.                                |           |

| 2      | What is the largest number of vertices in a graph with 35 edges, if a                          | 11 (3)    |

|        | vertices are of degree at least 3?                                                             |           |

| 3      | Define a Euler graph. Give an example of Eulerian graph which is no                            | ot (3)    |

|        | Hamiltonian                                                                                    |           |

| 4      | Give an example of a strongly connected simple digraph without a directe                       | d (3)     |

|        | Hamiltonian path.                                                                              |           |

| 5      | What is the sum of the degrees of any tree of $n$ vertices?                                    | (3)       |

| 6      | How many spanning trees are there for the following graph                                      | (3)       |

- Show that in a simple connected planar graph G having V-vertices, E-edges, (3) and no triangles  $E \le 3V 6$ .

- Let G be the following disconnected planar graph. Draw its dual  $G^*$ , and the dual  $G^*$ .

- 9 Consider the circuit matrix **B** and incidence matrix **A** of a simple connected (3) graph whose columns are arranged using the same order of edges. Prove that every row of **B** is orthogonal to every row of **A**?

- A graph is *critical* if the removal of any one of its vertices (and the edges (3) adjacent to that vertex) results in a graph with a lower chromatic number. Show that  $K_n$  is critical for all n > 1.

#### PART B

## Answer any one Question from each module. Each question carries 14 Marks

- 11 a) Prove that for any simple graph with at least two vertices has two vertices of (6) the same degree.

- b) Prove that in a complete graph with n vertices there are (n-1)/2 edge disjoint (8) Hamiltonian circuits and  $n \ge 3$

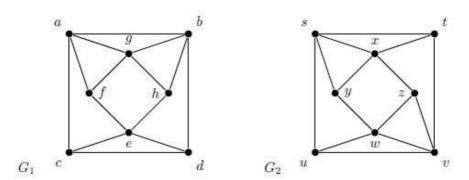

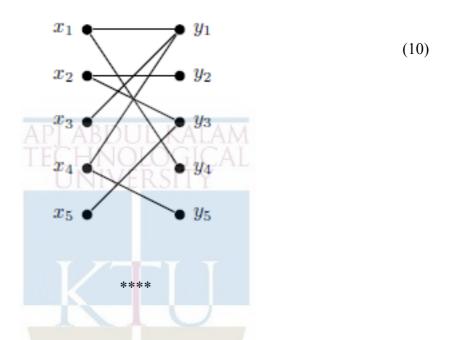

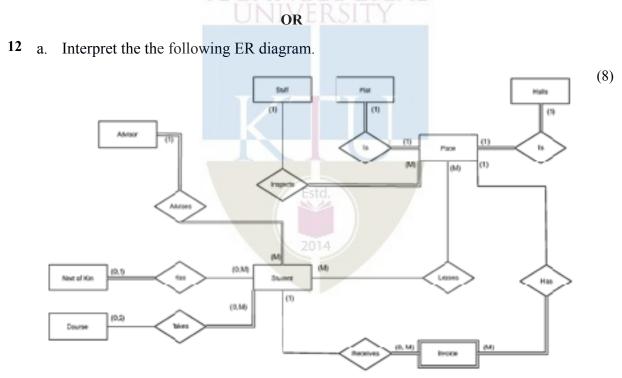

12 a) Determine whether the following graphs  $G_1 = (V_1, E_1)$  and  $G_2 = (V_2, E_2)$  are (6) isomorphic or not. Give justification.

- b) Prove that a simple graph with n vertices and k components can have at (8) most (n-k)(n-k+1)/2 edges

- 13 a) Let S be a set of 5 elements. Construct a graph G whose vertices are subsets (8) of S of size 2 and two such subsets are adjacent in G if they are disjoint.

- i. Draw the graph G.

- ii. How many edges must be added to **G** in order for **G** to have a Hamiltonian cycle?

- b) Let **G** be a graph with exactly two connected components, both being (6) Eulerian. What is the minimum number of edges that need to be added to **G** to obtain an Eulerian graph?

#### OR

- 14 a) Show that a k-connected graph with no hamiltonian cycle has an (8) independent set of size k + 1.

- i. Let G be a graph that has exactly two connected components, both being Hamiltonian graphs. Find the minimum number of edges that one needs to add to G to obtain a Hamiltonian graph.

- ii. For which values of n the graph  $Q_n$  (hyper-cube on n vertices) is Eulerian.

- 15 a) A tree *T* has at least one vertex *v* of degree 4, and at least one vertex *w* of (5) degree 3. Prove that *T* has at least 5 leaves.

# b) Write Dijkstra's shortest path algorithm.Consider the following weighted directed graph G.

(9)

Find the shortest path between a and every other vertices in G using Dijkstra's shortest path algorithm.

OR

- 16 a) Define pendent vertices in a binary tree? Prove that the number of pendent (5) vertices in a binary tree with n vertices is (n+1)/2.

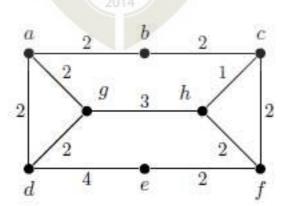

- b) Write Prim's algorithm for finding minimum spanning tree.

Find a minimum spanning tree in the following weighted graph, using Prim's algorithm.

Determine the number of minimum spanning trees for the given graph.

- 17 a) i. State and prove Euler's Theorem relating the number of faces, edges and (9) vertices for a planar graph.

- ii. If G is a 5-regular simple graph and |V| = 10, prove that G is non-planar.

- b) Let **G** be a connected graph and **e** an edge of **G**. Show that **e** is a cut-edge if (5) and only if **e** belongs to every spanning tree.

#### **OR**

18 a) State Kuratowski's theorem, and use it to show that the graph G below is not (9) planar. Draw G on the plane without edges crossing. Your drawing should use the labelling of the vertices given.

- b) Let **G** be a connected graph and **e** an edge of **G**. Show that **e** belongs to a (5) loop if and only if **e** belongs to no spanning tree.

- 19 a) Define the circuit matrix B(G) of a connected graph G with n vertices and e (7) edges with an example. Prove that the rank of B(G) is e-n+1

- b) Give the definition of the chromatic polynomial  $P_G(k)$ . Directly from the (7) definition, prove that the chromatic polynomials of  $W_n$  and  $C_n$  satisfy the identity  $P_{W_n}(k) = k P_{C_{n-1}}(k-1)$ .

#### **OR**

20 a) Define the incidence matrix of a graph G with an example. Prove that the rank of an incidence matrix of a connected graph with n vertices is n-1.

- b) i. A graph G has chromatic polynomial  $P_G(k) = k^4 4k^3 + 5k^2 2k$ . How many vertices and edges does G have? Is G bipartite? Justify your answers.

- ii. Find a maximum matching in the graph below and use Hall's theorem to show that it is indeed maximum.

# **Assignments**

Assignment must include applications of the above theory in Computer Science.

| Teaching Plan |                                                                                                        |                    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| No            | Topic                                                                                                  | No. of<br>Lectures |  |  |  |

| 1             | Module-I (Introduction to Graphs)                                                                      | (8)                |  |  |  |

| 1.            | Introduction- Basic definition – Application of graphs – finite and infinite graphs, bipartite graphs, | 1                  |  |  |  |

| 2.            | Incidence and Degree – Isolated vertex, pendent vertex and Null graph                                  | 1                  |  |  |  |

| 3.            | Paths and circuits                                                                                     | 1                  |  |  |  |

| 4.            | Isomorphism                                                                                            | 1                  |  |  |  |

| 5.            | Sub graphs, walks API ARDUI KALAM                                                                      | 1                  |  |  |  |

| 6.            | Paths and circuits                                                                                     | 1                  |  |  |  |

| 7.            | Connected graphs.                                                                                      | 1                  |  |  |  |

| 8.            | Disconnected graphs and components                                                                     | 1                  |  |  |  |

| 2             | Module-II (Eulerian and Hamiltonian graphs)                                                            | (8)                |  |  |  |

| 1.            | Euler graphs                                                                                           | 1                  |  |  |  |

| 2.            | Operations on graphs                                                                                   | 1                  |  |  |  |

| 3.            | Hamiltonian paths and circuits Estd                                                                    | 1                  |  |  |  |

| 4.            | Hamiltonian paths circuits                                                                             | 1                  |  |  |  |

| 5.            | Travelling salesman problem                                                                            | 1                  |  |  |  |

| 6.            | Directed graphs – types of digraphs,                                                                   | 1                  |  |  |  |

| 7.            | Digraphs and binary relation, Directed paths                                                           | 1                  |  |  |  |

| 8.            | Fleury's algorithm                                                                                     | 1                  |  |  |  |

| 3             | Module-III (Trees and Graph Algorithms)                                                                | (11)               |  |  |  |

| 1.            | Trees – properties                                                                                     | 1                  |  |  |  |

| 2.            | Trees – properties                                                                                     | 1                  |  |  |  |

| 3.            | Trees – properties, pendent vertex                                                                     | 1                  |  |  |  |

| 4.            | Distance and centres in a tree                                                                         | 1                  |  |  |  |

| 5.  | Rooted and binary tree                                              | 1   |

|-----|---------------------------------------------------------------------|-----|

| 6.  | Counting trees                                                      | 1   |

| 7.  | Spanning trees, Fundamental circuits                                | 1   |

| 8.  | Prim's algorithm                                                    | 1   |

| 9.  | Kruskal's algorithm                                                 | 1   |

| 10. | Dijkstra's shortest path algorithm                                  | 1   |

| 11. | Floyd-Warshall shortest path algorithm                              | 1   |

| 4   | Module-IV (Connectivity and Planar Graphs)                          | (9) |

| 1.  | Vertex Connectivity, Edge Connectivity                              | 1   |

| 2.  | Cut set and Cut Vertices                                            | 1   |

| 3.  | Fundamental circuits                                                | 1   |

| 4.  | Fundamental circuits                                                | 1   |

| 5.  | Planar graphs                                                       | 1   |

| 6.  | Kuratowski's theorem                                                | 1   |

| 7.  | Different representations of planar graphs                          | 1   |

| 8.  | Euler's theorem                                                     | 1   |

| 9.  | Geometric dual 2014                                                 | 1   |

| 5   | Module-V (Graph Representations and Vertex Colouring)               | (9) |

| 1.  | Matrix representation of graphs- Adjacency matrix, Incidence Matrix | 1   |

| 2.  | Circuit Matrix, Path Matrix                                         | 1   |

| 3.  | Colouring- chromatic number,                                        | 1   |

| 4.  | Chromatic polynomial                                                | 1   |

| 5.  | Matching                                                            | 1   |

| 6.  | Covering                                                            | 1   |

| 7.  | Four colour problem and five colour problem                         | 1   |

| 8. | Four colour problem and five colour problem | 1 |

|----|---------------------------------------------|---|

| 9. | Greedy colouring algorithm.                 | 1 |

| CST 202 | Computer<br>Organization<br>and Architecture | CATEGORY | L | Т | P | CREDIT | YEAR OF<br>INTRODUCTION |

|---------|----------------------------------------------|----------|---|---|---|--------|-------------------------|

|         |                                              | PCC      | 3 | 1 | 0 | 4      | 2019                    |

#### **Preamble:**

The course is prepared with the view of enabling the learners capable of understanding the fundamental architecture of a digital computer. Study of Computer Organization and Architecture is essential to understand the hardware behind the code and its execution at physical level by interacting with existing memory and I/O structure. It helps the learners to understand the fundamentals about computer system design so that they can extend the features of computer organization to detect and solve problems occurring in computer architecture.

Prerequisite: Topics covered under the course Logic System Design (CST 203)

Course Outcomes: After the completion of the course the student will be able to

| CO# | CO                                                                                      |

|-----|-----------------------------------------------------------------------------------------|

| CO1 | Recognize and express the relevance of basic components, I/O organization and           |

| COI | pipelining schemes in a digital computer (Cognitive knowledge: Understand)              |

| CO2 | Explain the types of memory systems and mapping functions used in memory systems        |

|     | (Cognitive Knowledge Level: Understand)                                                 |

| CO2 | Demonstrate the control signals required for the execution of a given instruction       |

| CO3 | (Cognitive Knowledge Level: Apply))                                                     |

| CO4 | Illustrate the design of Arithmetic Logic Unit and explain the usage of registers in it |

| CO4 | (Cognitive Knowledge Level: Apply)                                                      |

| COF | Explain the implementation aspects of arithmetic algorithms in a digital computer       |

| CO5 | (Cognitive Knowledge Level:Apply)                                                       |

| CO6 | Develop the control logic for a given arithmetic problem (Cognitive Knowledge           |

| CO6 | Level: Apply)                                                                           |

# Mapping of course outcomes with program outcomes

|     | PO1 | PO2 | PO3 | PO4 | PO5        | PO6 | PO7        | PO8      | PO9     | PO10 | PO11 | PO12 |

|-----|-----|-----|-----|-----|------------|-----|------------|----------|---------|------|------|------|

| CO1 |     |     |     |     |            |     |            |          |         |      |      |      |

| CO2 |     |     |     |     |            |     |            |          |         |      |      |      |

| CO3 |     |     |     |     |            |     |            |          |         |      |      |      |

| CO4 |     |     |     |     |            |     |            |          |         |      |      |      |

| CO5 |     |     |     | AP  | [ AB       | DUI | . KA       | LAN      |         |      |      |      |

| CO6 |     |     |     |     | 1HU<br>INU | VEF | OGI<br>SIT | CAI<br>Y | di<br>A |      |      |      |

|     | Abstract POs defined by National Board of Accreditation |      |                                |  |  |  |

|-----|---------------------------------------------------------|------|--------------------------------|--|--|--|

| РО# | Broad PO                                                | PO#  | Broad PO                       |  |  |  |

| PO1 | Engineering Knowledge                                   | PO7  | Environment and Sustainability |  |  |  |

| PO2 | Problem Analysis                                        | PO8  | Ethics                         |  |  |  |

| PO3 | Design/Development of solutions                         | PO9  | Individual and team work       |  |  |  |

| PO4 | Conduct investigations of complex problems              | PO10 | Communication                  |  |  |  |

| PO5 | Modern tool usage                                       | PO11 | Project Management and Finance |  |  |  |

| PO6 | The Engineer and Society                                | PO12 | Life long learning             |  |  |  |

# **Assessment Pattern**

| Plaam's Catagory | Continuous A | ssessment Tests | End Semester          |  |

|------------------|--------------|-----------------|-----------------------|--|

| Bloom's Category | Test1 (%)    | Test2 (%)       | Examination Marks (%) |  |

| Remember         | 20           | 20              | 30                    |  |

| Understand       | 40           | 40              | 30                    |  |

| Apply            | 40           | 40              | 40                    |  |

| Analyze          |              |                 |                       |  |

| Evaluate |  |  |

|----------|--|--|

| Create   |  |  |

## **Mark Distribution**

| Total Marks | CIE Marks | ESE Marks | ESE Duration |

|-------------|-----------|-----------|--------------|

| 150         | 50        | 100       | 3 hours      |

#### **Continuous Internal Evaluation Pattern:**

Attendance : 10 marks

Continuous Assessment Tests : 25 marks

Continuous Assessment Assignment : 15 marks

#### **Internal Examination Pattern:**

Each of the two internal examinations has to be conducted out of 50 marks

First Internal Examination shall be preferably conducted after completing the first half of the syllabus and the Second Internal Examination shall be preferably conducted after completing remaining part of the syllabus.

There will be two parts: Part A and Part B. Part A contains 5 questions (preferably, 2 questions each from the completed modules and 1 question from the partly covered module), having 3 marks for each question adding up to 15 marks for part A. Students should answer all questions from Part A. Part B contains 7 questions (preferably, 3 questions each from the completed modules and 1 question from the partly covered module), each with 7 marks. Out of the 7 questions in Part B, a student should answer any 5.

#### **End Semester Examination Pattern:**

There will be two parts; Part A and Part B. Part A contains 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which a student should answer any one. Each question can have maximum 2 sub-divisions and carries 14 marks.

#### **Syllabus**

#### Module 1

**Basic Structure of computers** – functional units - basic operational concepts - bus structures. Memory locations and addresses - memory operations, Instructions and instruction sequencing, addressing modes.

**Basic processing unit** – fundamental concepts – instruction cycle – execution of a complete instruction - single bus and multiple bus organization

#### Module 2

**Register transfer logic:** inter register transfer – arithmetic, logic and shift micro operations.

**Processor logic design:** - processor organization - Arithmetic logic unit - design of arithmetic circuit - design of logic circuit - Design of arithmetic logic unit - status register - design of shifter - processor unit - design of accumulator.

#### Module 3

**Arithmetic algorithms:** Algorithms for multiplication and division (restoring method) of binary numbers. Array multiplier, Booth's multiplication algorithm.

**Pipelining:** Basic principles, classification of pipeline processors, instruction and arithmetic pipelines (Design examples not required), hazard detection and resolution.

#### **Module 4**

**Control Logic Design:** Control organization – Hard\_wired control-microprogram control – control of processor unit - Microprogram sequencer,micro programmed CPU organization - horizontal and vertical micro instructions.

#### Module 5

**I/O organization:** accessing of I/O devices – interrupts, interrupt hardware -Direct memory access.

**Memory system:** basic concepts – semiconductor RAMs. memory system considerations – ROMs, Content addressable memory, cache memories - mapping functions.

#### **Text Books**

- 1. Hamacher C., Z. Vranesic and S. Zaky, Computer Organization ,5/e, McGraw Hill, 2011

- 2. Mano M. M., Digital Logic & Computer Design, PHI, 2004

- 3. KaiHwang, Faye Alye Briggs, Computer architecture and parallel processing McGraw-Hill, 1984

#### **Reference Books**

- 1. Mano M. M., Digital Logic & Computer Design, 3/e, Pearson Education, 2013.

- 2. Patterson D.A. and J. L. Hennessy, Computer Organization and Design, 5/e, Morgan Kaufmann Publishers, 2013.

- 3. William Stallings, Computer Organization and Architecture: Designing for Performance, Pearson, 9/e, 2013.

- 4. Chaudhuri P., Computer Organization and Design, 2/e, Prentice Hall, 2008.

- 5. Rajaraman V. and T. Radhakrishnan, Computer Organization and Architecture, Prentice Hall, 2011

#### **Sample Course Level Assessment Questions**

**Course Outcome1(CO1):** Which are the registers involved in a memory access operation and how are they involved in it?

**Course Outcome 2(CO2):** Explain the steps taken by the system to handle a write miss condition inside the cache memory.

**Course Outcome 3(CO3):** Generate the sequence of control signals required for the execution of the instruction MOV [R1],R2 in a threebus organization.

**Course Outcome 4(CO4):** Design a 4-bit combinational logic shifter with 2 control signals H0 and H1 that perform the following operations:

| H1 | Н0 | Operation                       |

|----|----|---------------------------------|

| 0  | 0  | Transfer 1's to all output line |

| 0  | 1  | No shift operation              |

| 1  | 0  | Shift left                      |

| 1  | 1  | Shift right                     |

Course Outcome 5(CO5): Explain the restoring algorithm for binary division. Also trace the algorithm to divide  $(1001)_2$  by  $(11)_2$

Course Outcome 6(CO6): Design a software control logic based on microprogramed control to perform the addition of 2 signed numbers represented in sign magnitude form.

#### **Model Question Paper**

| QP CODE: | PAGES:2 |

|----------|---------|

| Reg No:  |         |

| Name:    |         |

# APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY THIRD SEMESTER B.TECH DEGREE EXAMINATION, MONTH & YEAR

Course Code: CST 202

**Course Name:** Computer organization and architecture

Max.Marks:100 Duration: 3 Hours

#### PARTA

#### Answer all Questions. Each question carries 3 Marks

- 1. Give the significance of instruction cycle.

- 2. Distinguish between big endian and little endian notations. Also give the significance of these notations.

- 3. Compare I/O mapped I/O and memory mapped I/O.

- 4. Give the importance of interrupts in I/O interconnection.

- 5. Justify the significance of status register.

- 6. How does the arithmetic circuitry perform logical operations in an ALU.

- 7. Illustrate divide overflow with an example.

- 8. Write notes on arithmetic pipeline.

- 9. Briefly explain the role of micro program sequence.

- 10. Differentiate between horizontal and vertical micro instructions.

#### Part B

Answer any one Question from each module. Each question carries 14 Marks

| rchitecture.                  | 11.(a) What is the significance of addressing modes in computer arch                                                                                                                                                              |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (4)                           |                                                                                                                                                                                                                                   |

| in a three bus structure (10) | 11.(b) Write the control sequence for the instruction DIV R1,[R2] in                                                                                                                                                              |

|                               | OR                                                                                                                                                                                                                                |

| ram. Write the control        | Explain the concept of a single bus organization with help of a diagran sequence for the instruction ADD [R1],[R2].                                                                                                               |

| (14)                          |                                                                                                                                                                                                                                   |

| (14)                          | Explain various register transfer logics.                                                                                                                                                                                         |

| (11)                          | ORIVERSITI                                                                                                                                                                                                                        |

|                               |                                                                                                                                                                                                                                   |

|                               |                                                                                                                                                                                                                                   |

| nthesis are the values of     | 14.(a) Design a 4 bit combinational logic shifter with 2 control sign perform the following operations (bit values given in parenth control variable H1 and H2 respectively.): Transfer of 0's to shift left (10), no shift (11). |

| (5)                           | Sinte left (10), no sinte (11).                                                                                                                                                                                                   |

| _                             | 14.(b) Design an ALU unit which will perform arithmetic and logic binary adder.                                                                                                                                                   |

| (9)                           | 2014                                                                                                                                                                                                                              |

|                               |                                                                                                                                                                                                                                   |

|                               | 15.(a) Give the logic used behind Booth's multiplication algorithm.                                                                                                                                                               |

| (4)                           |                                                                                                                                                                                                                                   |

| n for the above input.        | 15.(b) Identify the appropriate algorithm available inside the sys multiplication between -14 and -9. Also trace the algorithm for                                                                                                |

| (10)                          | OR                                                                                                                                                                                                                                |

|                               |                                                                                                                                                                                                                                   |

|                               |                                                                                                                                                                                                                                   |

| sible solutions               | 16.(a) List and explain the different pipeline hazards and their possib                                                                                                                                                           |

| (10)                          |                                                                                                                                                                                                                                   |

|                               |                                                                                                                                                                                                                                   |

| 16.(b) Design a combinational circuit for 3x2 multiplication.                                                                           | 1)         |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

| 17. Design a hardwared control unit used to perform addition/subtraction of 2 numbers represented in sign magnitude form.               | <b>'</b> ) |

| (14                                                                                                                                     | <b>1</b> ) |

| OR                                                                                                                                      |            |

| 18. Give the structure of the micro program sequencer and its role in sequencing the micro instructions.                                | O          |

| (14                                                                                                                                     | 1)         |

| 19. (a) Explain the different ways in which interrupt priority schemes can be implemented (10. 19.(b)) Give the structure of SRAM cell. | ))         |

| OR                                                                                                                                      |            |

| 20.                                                                                                                                     |            |

| 20.(a) Explain the various mapping functions available in cache memory.                                                                 | •)         |

| 20.(b) Briefly explain content addressable memory.                                                                                      | 5)         |

| TEACHING PLAN |                                                                             |                         |  |

|---------------|-----------------------------------------------------------------------------|-------------------------|--|

| No            | Contents                                                                    | No of<br>Lecture<br>Hrs |  |

|               | Module 1: (Basic Structure of computers) (9 hours)                          |                         |  |

| 1.1           | Functional units,basic operational concepts,bus structures (introduction)   | 1                       |  |

| 1.2           | Memory locations and addresses, memory operations                           | 1                       |  |

| 1.3           | Instructions and instruction sequencing                                     | 1                       |  |

| 1.4           | Addressing modes                                                            | 1                       |  |

| 1.5           | Fundamental concepts of instruction execution, instruction cycle            | 1                       |  |

| 1.6           | Execution of a complete instruction - single bus organization (Lecture 1)   | 1                       |  |

| 1.7           | Execution of a complete instruction - single bus organization (Lecture 2)   | 1                       |  |

| 1.8           | Execution of a complete instruction - multiple bus organization (Lecture 1) | 1                       |  |

| 1.9           | Execution of a complete instruction - multiple bus organization (Lecture 2) | 1                       |  |

|               | Module 2: (Register transfer logic and Processor logic design) (10 h        | ours)                   |  |

| 2.1           | Inter register transfer – arithmetic micro operations                       | 1                       |  |

| 2.2           | Inter register transfer – logic and shift micro operations                  | 1                       |  |

| 2.3           | Processor organization                                                      | 1                       |  |

| 2.4           | Design of arithmetic circuit                                                | 1                       |  |

| 2.5           | Design of logic circuit                                                     | 1                       |  |

| 2.6           | Design of arithmetic logic unit                                             | 1                       |  |

| 2.7           | Design of status register                                                   | 1                       |  |

| 2.8           | Design of shifter - processor unit                                          | 1                       |  |

| 2.9 Design of accumulator (Lecture 1)  2.10 Design of accumulator (Lecture 2)  1  Module 3: (Arithmetic algorithms and Pipelining) (9 hours)  3.1 Algorithm for multiplication of binary numbers  1  3.2 Algorithm for division (restoring method) of binary numbers  1  3.3 Array multiplier  1  3.4 Booth's multiplication algorithm  1  3.5 Pipelining: Basic principles  3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  1  3.9 Hazard detection and resolution  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization—design of hardwired control logic (Lecture 1)  4.2 Control organization—design of hardwired control logic (Lecture 2)  4.3 Control organization—design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic—control of processor unit (Lecture1)  4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  5.1 Accessing of I/O devices—interrupts  5.2 Interrupt hardware |      |                                                                           |   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------|---|--|--|

| Module 3 : (Arithmetic algorithms and Pipelining) (9 hours)  3.1 Algorithm for multiplication of binary numbers 1  3.2 Algorithm for division (restoring method) of binary numbers 1  3.3 Array multiplier 1  3.4 Booth's multiplication algorithm 1  3.5 Pipelining: Basic principles 1  3.6 Classification of pipeline processors (Lecture 1) 1  3.7 Classification of pipeline processors (Lecture 2) 1  3.8 Instruction and arithmetic pipelines (Design examples not required) 1  3.9 Hazard detection and resolution 1  Module 4 : (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1) 1  4.2 Control organization –design of hardwired control logic (Lecture 2) 1  4.3 Control organization –design of hardwired control logic (Lecture 3) 1  4.4 Design of microprogram control logic–control of processor unit (Lecture1) 1  4.5 Design of microprogram control logic–control of processor unit (Lecture2) 1  4.6 Design of microprogram control logic–control of processor unit (Lecture3) 1  4.7 Microprogram sequencer 1  4.8 Micro programmed CPU organization 1  4.9 Microinstructions –horizontal and vertical micro instructions 1  Module 5 : (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts 1              | 2.9  | Design of accumulator (Lecture 1)                                         | 1 |  |  |

| 3.1 Algorithm for multiplication of binary numbers  3.2 Algorithm for division (restoring method) of binary numbers  1 3.2 Algorithm for division (restoring method) of binary numbers  1 3.3 Array multiplier  3.4 Booth's multiplication algorithm  1 3.5 Pipelining: Basic principles  3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  1 3.9 Hazard detection and resolution  1  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization—design of hardwired control logic (Lecture 1)  4.2 Control organization—design of hardwired control logic (Lecture 2)  4.3 Control organization—design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic—control of processor unit (Lecture1)  4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts                                         | 2.10 | Design of accumulator (Lecture 2)                                         | 1 |  |  |

| 3.2 Algorithm for division (restoring method) of binary numbers  3.3 Array multiplier  3.4 Booth's multiplication algorithm  3.5 Pipelining: Basic principles  3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  3.9 Hazard detection and resolution  1 Module 4: (Control Logic Design) (9 hours)  4.1 Control organization—design of hardwired control logic (Lecture 1)  4.2 Control organization—design of hardwired control logic (Lecture 2)  4.3 Control organization—design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic—control of processor unit (Lecture1)  4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts                                                                                                                                                                          |      | Module 3: (Arithmetic algorithms and Pipelining) (9 hours)                |   |  |  |

| 3.3 Array multiplier  3.4 Booth's multiplication algorithm  3.5 Pipelining: Basic principles  3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  3.9 Hazard detection and resolution  1 Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 2)  4.4 Design of microprogram control logic –control of processor unit (Lecture1)  4.5 Design of microprogram control logic –control of processor unit (Lecture2)  4.6 Design of microprogram control logic –control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  1 Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                 | 3.1  | Algorithm for multiplication of binary numbers                            | 1 |  |  |

| 3.4 Booth's multiplication algorithm  3.5 Pipelining: Basic principles  1 3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  1 3.9 Hazard detection and resolution  1  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                       | 3.2  | Algorithm for division (restoring method) of binary numbers               | 1 |  |  |

| 3.5 Pipelining: Basic principles  3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  1  3.9 Hazard detection and resolution  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic—control of processor unit (Lecture1)  4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts                                                                                                                                                                                                                                                                                                | 3.3  | Array multiplier                                                          | 1 |  |  |

| 3.6 Classification of pipeline processors (Lecture 1)  3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  3.9 Hazard detection and resolution  1 Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                    | 3.4  | Booth's multiplication algorithm                                          | 1 |  |  |

| 3.7 Classification of pipeline processors (Lecture 2)  3.8 Instruction and arithmetic pipelines (Design examples not required)  3.9 Hazard detection and resolution  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                             | 3.5  | Pipelining: Basic principles                                              | 1 |  |  |

| 3.8 Instruction and arithmetic pipelines (Design examples not required)  3.9 Hazard detection and resolution  1  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.6  | Classification of pipeline processors (Lecture 1)                         | 1 |  |  |

| 3.9 Hazard detection and resolution  Module 4: (Control Logic Design) (9 hours)  4.1 Control organization – design of hardwired control logic (Lecture 1)  4.2 Control organization – design of hardwired control logic (Lecture 2)  4.3 Control organization – design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions – horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.7  | Classification of pipeline processors (Lecture 2)                         | 1 |  |  |

| Module 4 :( Control Logic Design) (9 hours)  4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5 : (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.8  | Instruction and arithmetic pipelines (Design examples not required)       | 1 |  |  |

| 4.1 Control organization –design of hardwired control logic (Lecture 1)  4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.9  | Hazard detection and resolution                                           | 1 |  |  |

| 4.2 Control organization –design of hardwired control logic (Lecture 2)  4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | Module 4 : (Control Logic Design) (9 hours)                               |   |  |  |

| 4.3 Control organization –design of hardwired control logic (Lecture 3)  4.4 Design of microprogram control logic–control of processor unit (Lecture1)  4.5 Design of microprogram control logic–control of processor unit (Lecture2)  4.6 Design of microprogram control logic–control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.1  | Control organization –design of hardwired control logic (Lecture 1)       | 1 |  |  |

| 4.4 Design of microprogram control logic—control of processor unit (Lecture1)  4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.2  | Control organization –design of hardwired control logic (Lecture 2)       | 1 |  |  |

| 4.5 Design of microprogram control logic—control of processor unit (Lecture2)  4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.3  | Control organization –design of hardwired control logic (Lecture 3)       | 1 |  |  |

| 4.6 Design of microprogram control logic—control of processor unit (Lecture3)  4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions—horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices—interrupts  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.4  | Design of microprogram control logic-control of processor unit (Lecture1) | 1 |  |  |

| 4.7 Microprogram sequencer  4.8 Micro programmed CPU organization  4.9 Microinstructions –horizontal and vertical micro instructions  1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5  | Design of microprogram control logic-control of processor unit (Lecture2) | 1 |  |  |

| 4.8 Micro programmed CPU organization 1  4.9 Microinstructions –horizontal and vertical micro instructions 1  Module 5: (Basic processing units, I/O and memory) (8 hours)  5.1 Accessing of I/O devices –interrupts 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.6  | Design of microprogram control logic–control of processor unit (Lecture3) | 1 |  |  |